들어가며

전자, IT 등 하이테크 산업의 근간이 되는 반도체는 현존하는 모든 최첨단 기술이 집약된 제품이라 해도 과언이 아닙니다. 이는 반도체를 생산하기 위한 공정, 장비, 소재 등 물리적인 영역뿐만 아니라 설계·검증을 위한 소프트웨어 분야도 마찬가지입니다. 반도체 설계·검증은 EDA(Electronic Design Automation) 도구들을 이용하여 많은 부분 자동화되었습니다. 시장 또한 성장세를 보이고 있는데, 전 세계 기준 2020년 11조 원 규모에서 2027년까지 연평균 9.6% 성장하여 23조 원에 이를 것으로 전망됩니다.

반도체 산업은 글로벌 기업 간의 기술 및 투자 경쟁이 매우 치열한 분야입니다. 이러한 경쟁에서 가장 중요한 요소는 Time-To-Market과 수율입니다. 제품을 시장에 빨리 내놓을수록 일종의 선점·독점 효과를 누리게 되며 양산 수율은 그대로 이익과 직결됩니다. 얼마나 빨리 제품을 생산해 경쟁력 있는 수율을 달성하는가에 모든 사활이 걸려 있는 것입니다.

반도체 공정은 갈수록 미세화가 진행되어 메모리 용량이나 CPU 속도가 18개월마다 2배씩 증가한다는 무어의 법칙이 여전히 유효함을 보여주고 있습니다. 이렇게 집적도가 증가하면서 EDA 도구들이 처리해야 할 데이터의 양과 복잡도도 같이 증가하고 있으며 생산 가능한 설계(DFM : Design For Manufacturability)를 도출하는 것이 갈수록 어려워지고 있습니다. 이를 극복하고자 반도체 산업은 다양한 혁신을 시도하고 있으며 최신 IT 트렌드와도 큰 연관성이 있습니다.

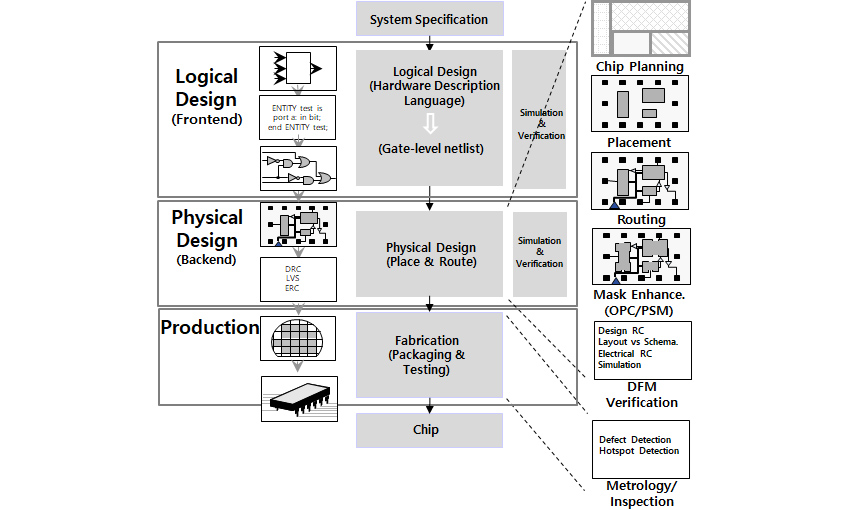

반도체 설계 과정

- system Specification

- Logical Design(hardware description language)-(gate-level nestlist)

- Physical Design(place & route)

- fabrication(package & testing)

- chip

(출처: VLSI Physical Design: From Graph Partitioning to Timing Closure)

반도체 설계 과정은 많은 부분에서 소프트웨어 개발과 유사합니다. 반도체 칩의 사양(Specification)을 정하고 HDL(High-Level Description Language)로 불리는 프로그래밍 언어를 사용하여 칩의 동작 방식을 기술합니다. HDL은 VHDL, Verilog, System C가 대표적이며, 소프트웨어 개발용 프로그래밍 언어와 크게 다르지 않습니다. 이렇게 개발된 소스코드는 컴파일러를 통하여 RTL(Register Transfer Level)로 변환되며 일종의 IL(Intermediate Language) 혹은 목적 코드(Object Code)에 해당합니다. RTL 코드는 최종적으로 넷리스트(Netlist)로 변환되는데 반도체의 기본소자인 게이트(Gate) 간의 연결 관계를 표현하는 것으로 결국 논리적인 회로도(Schematic)를 나타냅니다. HDL에서 넷리스트로 변환하는 과정을 논리 합성(Logical Synthesis)이라고 합니다.

논리 합성을 거쳐 생성된 넷리스트는 의도한 대로 동작하는지 검증(Verification)하는 단계를 거칩니다. 검증이 완료된 넷리스트는 P&R(Placement & Route) 과정을 거쳐 물리적인 도면(Physical Layout)으로 변환됩니다. P&R은 넷리스트상의 단위소자인 라이브러리(Library)를 배치(Placement)하고 핀(Pin)들이 연결되도록 배선(Route)하는데 이때 주어진 디자인 제약조건(Design Constraint)을 충족하는 배치와 배선 경로를 탐색해야 하기 때문에 매우 복잡한 문제를 풀어야 합니다. 디자인 제약조건은 예를 들면 칩의 면적을 한정하거나 배선의 최대 길이를 제한하거나 하는 규칙들입니다. 배선이 길면 핀 간 배선의 저항에 의해 전입이 떨어져 회로가 정상 동작을 하지 못하며 신호가 지연되어 타이밍 문제를 일으킵니다.

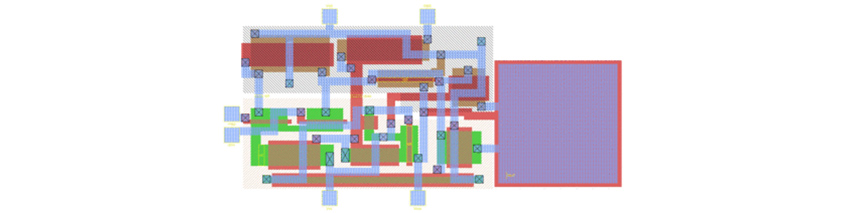

P&R 과정을 거치면 물리적인 도면이 생성되며 이는 GDS(Graphics Design System) 형식의 파일로 저장되는데 이 과정을 물리 합성(Physical Synthesis)이라고 합니다.

[그림 2] GDS 파일 렌더링

[그림 2] GDS 파일 렌더링(출처: https://en.wikipedia.org/wiki/Integrated_circuit_design)>

GDS 파일은 반도체의 물리적인 형상을 레이어(Layer)와 폴리곤(Polygon)을 이용하여 표현합니다. GDS 파일은 70년대에 제정된 표준으로 현재는 OASIS라고 불리는 새로운 형식의 파일로 점차 대체되고 있지만 실무에서는 구분 없이 통칭하여 GDS라고 부릅니다. GDS 파일은 PDF와 같은 벡터 그래픽 파일과 유사한 형식이지만 베지에 곡선(Bezier Curve)이나 폰트(Font) 같은 복잡한 요소는 배제되고 Rectangle, Polygon, Path 같은 기본적인 도형 요소들로 구성됩니다. 이러한 요소들의 집합이 셀(Cell)이라고 불리는 단위로 정의되어 있으며 셀을 반복 배치하거나 계층으로 구성하여 작은 크기의 데이터로 복잡한 도면을 표현합니다. 최신 반도체 칩의 경우 수조 개 이상의 폴리곤이 저장될 정도로 대용량인 경우가 많고 용량은 수백 GB에 이르기도 합니다. 때문에 이러한 파일을 처리하기 위해서는 Out-Of-Core 알고리즘에 대한 고려가 필요하며 효율적인 Spatial Acceleration 아키텍처를 설계하여 요소에 대한 접근을 최적화해야 합니다.

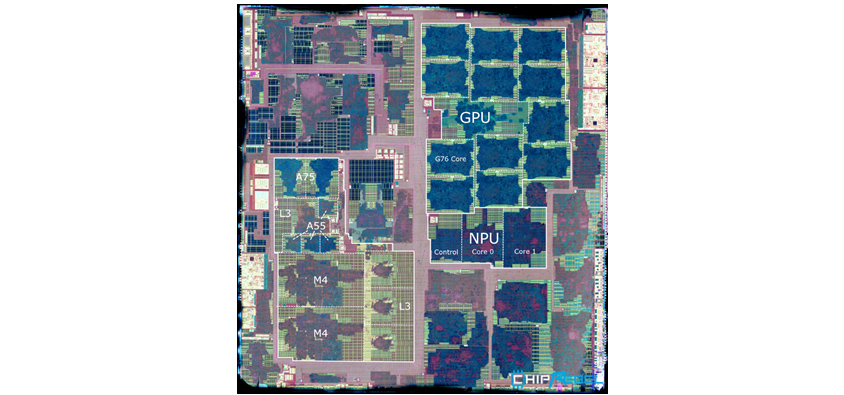

[그림 3] Exynos 9820 Die Photo

[그림 3] Exynos 9820 Die Photo(출처: https://www.chiprebel.com/exynos-9820)

이렇게 생성된 GDS 파일은 DRC(Design Rule Check) 및 LVS(Layout vs. Schematic) 검증 과정을 거칩니다. DRC는 물리적인 형상이 만족해야 할 규칙을 검증하는 과정으로 예를 들면 Gate와 Metal이 Contact과 영역이 겹치는지 (따라서 물리적으로 접촉되었는지) 검사하는 규칙 등이 있습니다. LVS는 물리적인 형상으로부터 거꾸로 논리적인 회로 (Schematic)를 재건(Reconstruction)하여 원래의 회로와 같은지 검증하는 과정입니다.

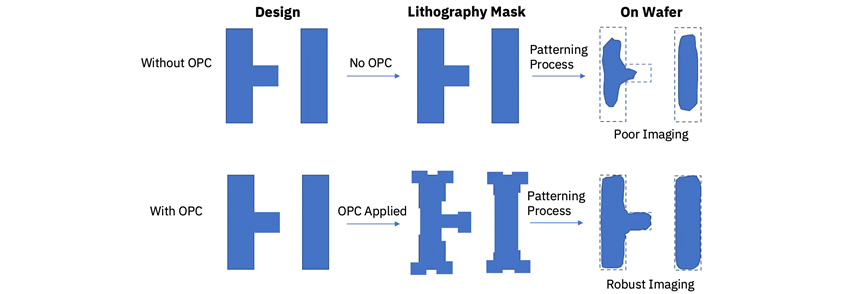

물리적인 설계 이후에는 생산 가능한 설계(DFM : Design For Manufacture)를 도출하기 위한 단계를 거칩니다. P&R을 통하여 산출한 도면은 웨이퍼 표면에 형성되어야 하는 타깃 패턴(Target Pattern)이며, 실제로 웨이퍼에 이러한 타깃 패턴을 형성하는 것은 또 다른 험난한 과정입니다. 웨이퍼 패터닝은 감광 물질(포토레지스트, Photoresist)을 도포한 후 포토마스크라고 불리는 패턴이 새겨진 유리판에 빛을 통과시켜 빛을 받은 부분과 받지 못한 부분이 다르게 화학 반응을 하도록 현상하고(Develop) 선택적으로 패턴을 녹여내는 에칭(Etching) 과정을 거쳐 생성됩니다. 이때 빛의 회절 현상이나 포커스 값과 화학 반응의 정도에 따른 변수 등이 작용하여 의도한 패턴 형성을 방해하게 됩니다. 이러한 현상을 극복하기 위해서 OPC(Optical Proximity Correction) 같은 기법을 동원하여 타깃 패턴에 가깝게 형성되도록 하는 포토마스크 패턴을 역으로 계산하는 과정을 거치기도 합니다.

- without OPC

- with OPC

- No OPC

- OPC Applied

- Patterning Process

- Patterning Process

- Poor Imaging

- Robust Imaging

(출처: https://www.ibm.com/cloud/blog/ibm-and-synopsys-demonstrate-euv-opc-workload-runs-11000-cores-on-the-hybrid-cloud)

양산에 들어가기 전 마지막 단계를 MTO(Mask Tape Out)라고 하며 모든 검증이 완료된 후 생산에 들어갑니다. 양산 과정에서도 수율 확보를 위한 다양한 활동을 하는데 대표적인 예로 MI(Metrology & Inspection)를 들 수 있습니다. MI는 광학현미경이나 SEM/TEM (Scanning/Transmission Electronic Microscope) 같은 전자현미경을 동원하여 불량 발생을 모니터링합니다. 발견된 불량은 이물질이나 공정 외적인 요소로 인해 발생한 불량(Random Defect)인지 설계상 취약점으로 인해 발생하는 불량(Systematic Defect)인지 판별하고 근본 원인(Root Cause)에 대한 분석을 진행합니다.

[그림 5] Various defect patterns

[그림 5] Various defect patterns(출처: http://www.ddaily.co.kr/cloud/news/article.html?no=149274)

EDA 소프트웨어의 장벽

EDA 소프트웨어는 실로 오랜 역사를 가지고 있는 분야입니다. 대표적으로 EDA 빅3로 불리는 시놉시스(Synopsys), 케이던스(Cadence), 지멘스EDA(구 Mentor Graphics)와 같은 회사는 30년 이상의 역사를 가지고 있습니다. EDA 소프트웨어를 개발하기 위해서는 반도체 산업에 대한 전문 지식이 필요하며 최고 수준의 소프트웨어 개발 역량도 갖춰야 합니다. 또한 컴파일러 기술부터 Physical Layout을 처리하기 위한 Computational Geometry, 물리 시뮬레이션을 위한 광학이나 전자기학 등 실로 다양한 기술이 요구됩니다. EDA 빅3의 제품들은 오랜 기간 사용되면서 발전해왔고 반도체 산업의 표준 도구로 자리잡고 있습니다.

이러한 환경에서 후발 주자가 새로운 소프트웨어 제품을 보급하는 것은 쉬운 일이 아닙니다. 기술 격차를 극복하는 것도 어렵거니와 반도체 업체가 새로운 소프트웨어를 사용함으로써 발생하는 리스크를 감수할 이유가 없기 때문입니다. 그렇기 때문에 EDA 분야의 신생업체들은 새로운 혁신적인 기술을 기반으로 하는 경우가 많습니다. EDA 빅3는 이러한 매력적인 소규모 업체들을 인수하여 자사 제품에 반영함으로써 기술적 우위를 유지하는 전략을 사용하고 있습니다.

EDA 소프트웨어 트렌드

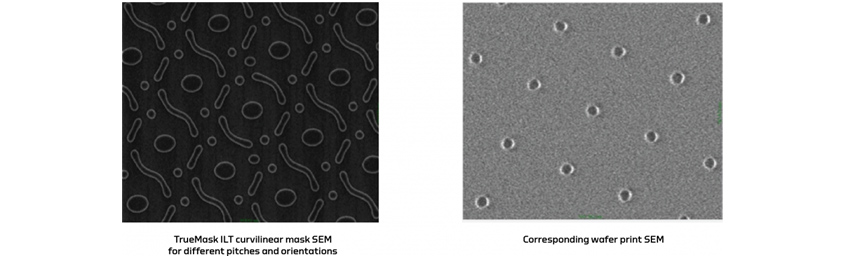

EDA 분야는 새로운 혁신적인 방식들을 도입해가면서 지속적인 발전을 이루고 있습니다. 전통적인 직선 위주의 포토마스크 패턴에서 곡선 형태(Curvilinear)의 패턴을 사용하여 해상도를 더욱 높이는 시도는 상용화가 머지 않은 기술입니다. 포토마스크 제작은 크롬 코팅된 유리판에 레이저 빛을 이용하여 패턴을 새기는데 기존 방식으로는 복잡한 패턴의 마스크를 제작하는데 한계가 있었습니다. 보통 Manhattan Geometry라고 불리는 직각 패턴만 가능했으나 VSB(Variable Shaped Beam)나 Multi-Beam Mask Writer가 등장하면서 다양한 모양의 패턴을 마스크에 프린트하는 게 가능해졌습니다. 이에 따라 기존 직각 위주의 설계 방식에서 Any Angle 더 나아가 곡선 형태의 패턴을 지원하는 새로운 설계 방식이 연구되고 있습니다.

ILT(Inverse Lithography) 기술은 이러한 Curvilinear 마스크를 위한 가장 중요한 기술에 속합니다. ILT는 OPC(Optical Proximity Correction) 방식 중 하나입니다. Conventional한 OPC는 패턴의 Edge를 잘게 쪼개어 상하좌우로 이동하거나 사각형 형태의 Assist Feature를 규칙 기반으로 삽입하여 회절에 의한 왜곡을 보정하는 방식으로 동작합니다. 포토마스크에서 웨이퍼 표면으로 전사되는 이미지를 계산하는 것은 광학계를 수학적으로 표현하여 얻을 수 있습니다. 이를 Forward Function이라고 하며 ILT는 이 Forward Function의 Inverse Function을 구하려는 시도입니다. ILT는 이미 구현되어 있는 기술이지만 매우 많은 연산을 필요로 하기 때문에 전체 칩(Full Chip ILT)에 적용하기보다는 국소적으로 패턴이 복잡한 곳에 사용하는 방식으로 활용되었습니다. 하지만 최근 GPU 클러스터를 기반으로 기존 OPC 수준의 처리 속도를 확보한 Full Chip ILT 기술이 등장하면서 Curvilinear 마스크 활용이 더욱 가까워지고 있습니다.

[그림 6] Curvilinear mask and corresponding wafer pattern

[그림 6] Curvilinear mask and corresponding wafer pattern(출처: https://design2silicon.com/products/truemask-ilt)

설계 과정 곳곳에서 AI를 활용하려는 노력이 지속되고 있습니다. 구글은 강화학습(Reinforcement Learning)을 P&R 및 Floor Planning에 적용한 결과를 발표하기도 하였으며, 시놉시스, 케이던스에서도 딥러닝을 활용한 제품들이 출시되고 있습니다. 반도체 설계에 AI 활용이 점차 활성화되면서 그에 필요한 데이터를 체계적으로 관리·분석하기 위한 플랫폼, 컴퓨팅 클러스터에 대한 요구사항도 지속적으로 증가하고 있습니다.

반도체 설계 과정에서는 실제 물리적인 공정을 그대로 표현하는 모델을 생성하여 주어진 설계에 대한 결과값을 예측하는 화이트박스 모델링 기법을 주로 사용합니다. 대표적으로 OPC에서는 포토마스크 패턴이 웨이퍼 표면에 형성되는 광학계를 모델링하거나 감광 물질이 빛과 반응하는 과정, 에칭 과정을 모델링하게 되는데 이러한 모델과 실제 물리적인 공정 간의 오차를 줄이기 위해 테스트 패턴을 웨이퍼로 제작한 후 CD-SEM(Critical Dimension Scanning Electronic Microscope)으로 관측하여 오차를 보정(Calibration)하는 과정을 거치게 됩니다. 이렇게 생성된 촬영 이미지는 주어진 공정값에 대한 설계 패턴의 실제 물리적인 웨이퍼 형태를 표현하는 것으로 AI 활용 가능성이 큰 데이터입니다.

또 하나의 중요한 트렌드는 오픈화입니다. 오픈화 경향은 반도체 설계 자산에 대한 오픈화 및 반도체 설계 과정에 대한 오픈화가 모두 이루어지고 있습니다. 대표적인 오픈 반도체 설계 자산은 RISC-V가 있습니다. RISC-V는 ARM, 인텔, AMD 등의 전유물이었던 CPU에 새로운 명령어 체계(Instruction Set Architecture) 및 설계 IP, 그에 따른 표준 공정들을 제공합니다. 오픈소스 소프트웨어와 유사한 형태로 하드웨어 설계에서의 오픈화 시도이며 RISC-V 기반의 업체들이 활발하게 생겨나고 인수·합병도 이루어지고 있습니다. 또한 이에 대한 공정을 개발하기 위한 오픈소스 PDK(Process Development Kit)도 구글에 의해서 실험적으로 진행되고 있습니다. 오픈화 자산들은 반도체 제조의 진입 장벽을 낮추기 위한 꾸준한 노력을 통하여 오픈소스 소프트웨어처럼 중요한 역할을 할 것으로 기대됩니다.

HPC에 대한 요구사항도 중요한 문제입니다. 반도체 설계가 갈수록 복잡해지고 이에 필요한 컴퓨팅 파워 및 스토리지 요구사항도 지속적으로 증가하는 추세입니다. 최신 칩 설계의 경우 OPC 과정을 수행하는데 수천 코어를 사용하여 수십 시간이 걸리기도 합니다. 이러한 컴퓨팅 자원들을 효율적으로 관리하고 유지하는데 매우 큰 비용이 들어갑니다. 클라우드 전환은 자연스러운 것처럼 보이지만 사실 반도체 분야는 보안이 매우 중요하게 작용하고 있습니다. 자신의 설계 데이터가 클라우드에 업로드되는 것을 고객들은 원하지 않습니다. 보안 문제가 가장 큰 걸림돌이지만 그럼에도 불구하고 클라우드를 활용하는 움직임은 실제로 일어나고 있습니다. 주요 반도체 제조사들은 클라우드상에서 설계·검증할 수 있는 서비스를 제공합니다.

마치며

반도체 산업이 많은 주목을 받고 있는 것에 비해 EDA 소프트웨어는 다소 생소한 분야입니다. 하지만 갈수록 치열해지는 기술 경쟁 속에서 EDA 소프트웨어의 역할이 더욱 중요해지고 혁신적인 기술에 대한 요구도 높아지고 있습니다. 본 아타클을 통하여 EDA 소프트웨어에 대한 이해를 넓히고 그 속에서 다양한 관점과 인사이트를 얻을 수 있기를 바랍니다.

# References

[1] VLSI Physical Design: From Graph Partitioning to Timing Closure / 2011 / Springer

- https://github.com/google/skywater-pdk

- https://www.alliedmarketresearch.com/electronic-design-automation-software-market

▶ 해당 콘텐츠는 저작권법에 의하여 보호받는 저작물로 기고자에게 저작권이 있습니다.

▶ 해당 콘텐츠는 사전 동의 없이 2차 가공 및 영리적인 이용을 금하고 있습니다.

![]()

에스코어(주) 기술그룹

Computational Geometry & Graphics 기반 역량과 반도체 도메인 지식을 바탕으로 다양한 EDA 관련 프로젝트를 진행하고 있습니다.